1、网页中按钮的常见类型有哪些? 2、网页中按钮的特点有哪些? 3、按钮的设计要点有哪些?一、网页中按钮的常见类型:1、静态图片按钮将按钮制作为静态图片的效果,不带有任何的交互

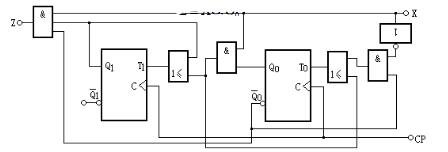

求一个,8进制同步时序逻辑电路设计

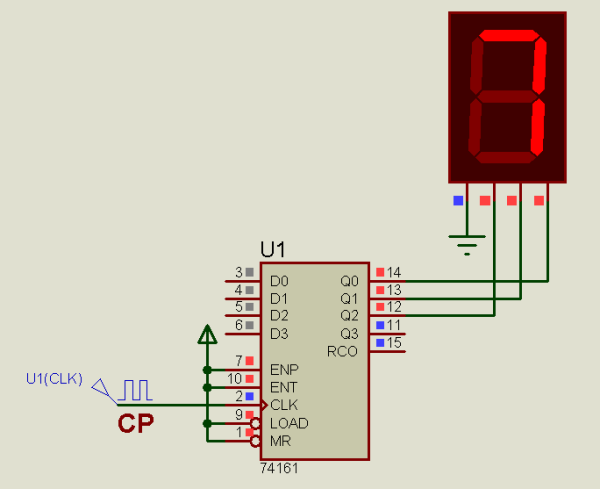

同步时序逻辑电路设计用74161制成8进制的计数器

用74161做8进制的计数器,即不用清0法,也不用置数法。因为74161就是四位二进制计数器,即16进制计数器,四位输出为0000~1111。那么取低3位输出端,Q2Q1Q0就是8进制二进制数,即000~111。将74161接成正常计数状态,取低3位即可。如下仿真图所示,最高位Q3不用。数码管可省掉,那是为了显示仿真效果的。

同步时序逻辑电路的设计步骤是什么?

1.根据具体问题,进行逻辑抽象,列出状态表或状态图 2.状态化简 3.状态编码 4.确定触发器的类型 5.写出状态方程,输出方程和驱动方程 6.画出逻辑电路图 7.检查设计电路能否自启动设计同步时序逻辑电路的一般步骤有哪些

同步计数器设计的一般步骤为:

1、分析设计要求,确定触发器数目和类型;

2、选择状态编码;

3、求状态方程,驱动方程;

4、根据驱动方程画逻辑图;

5、检查能否自启动。

扩展资料

1、一个触发器有两个稳定状态:

“0”状态:Q=0,=1;

“1”状态:Q=1,=0。

2、触发器(FF)应具有以下功能:

在新数据输入之前(无触发信号)时,触发器一直保持原来的状态(原数据)不变。

输入信号触发下,它能从一种状态转换为另一种状态。即:FF能够“接收”“保持”并“输出”数字信息。

时序电路的时序电路的设计

钟控时序逻辑电路的设计从一组规格说明书开始,继而得到逻辑图或一系列布尔函数,再从中生成逻辑图。时序电路和组合电路的不同之处在于,组合电路定义完全由真值表定义,而时序逻辑电路需要用状态表定义。所以,时序电路设计的第一步就是得到状态,或和状态具有相同信息表达能力的其它逻辑表示形式,如状态图等。

同步时序电路是由触发器和组合门组成的。电路设计包括选择触发器和设计组合逻辑结构,保证这个组合逻辑结构和触发器组成的电路可以实现状态规格说明书中的预期目标。所需触发器的最小个数是由电路状态的个数决定的;n个触发器可以表示2^n个二进制状态。组合电路是通过计算触发器的输入方程和输出方程从状态表中得到的。实际上,一旦触发器的类型和数量确定或,设计步骤就由对一个时序电路的设计转换为一个组合电路的设计。用这种方法,就可以使用组合电路设计技术。 下面提到的时序电路的设计步骤与组合电路类似,但还需要一些额外的步骤。

1.规格说明书:如果没有,先写出电路的规格说明书。

2.系统描述:从问题的陈述中得出状态图或状态表。

3.状态赋值:如果通过步骤1中只能得到状态图,则在从状态图中得到状态表。并未状态表中的每个状态赋二进制代码。

4.得到触发器的输入方程:选择一种或多种类型的触发器,通过已经编码的状态表中的下一状态得到触发器的状态方程。

5.得到输出方程:通过状态表中的输出信号栏得到输出方程。

6.优化:优化触发器的输入方程和输出方程。

7.工艺映射:画出电路由触发器、与门、或门和反向器所组成的逻辑图。将这个逻辑图转换为由有效的触发器和门工艺组成的新的逻辑图。

8.验证:验证最终设计的正确性。

为了方便起见,我们一般都省略步骤7即工艺映射,而在示意图中仅使用触发器、与门、或门和反向器。

时序逻辑电路有哪些

时序逻辑电路有以下3种:

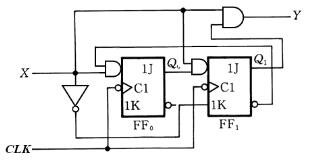

1、时序逻辑电路的设计(一)

下图的时序逻辑电路是:设计一个串行数据检测器,对它的要求是:连续输入3个或3个以上的1时输出为1,其他输入情况下输出为0。

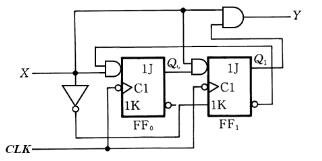

2、时序逻辑电路的设计(二)

下图的时序逻辑电路是:试用JK触发器和门电路设计一个同步七进制计数器。

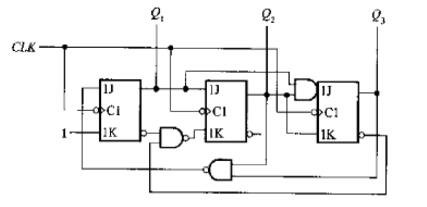

3、时序逻辑电路的设计(三)

下图的时序逻辑电路是:设计一“011”序列检测器,每当输入011码时,对应最后一个1,电路输出为1。

扩展资料:

时序逻辑电路的特点:

1、功能特点:电路在某采样周期内的稳态输出Y(n),不仅取决于该采样周期内的“即刻输入X(n)”,而且还与电路原来的状态Q(n)有关。(通常Q(n)记录了以前若干周期内的输入情况)

2、结构特点:除含有组合电路外,时序电路必须含有存储信息的有记忆能力的电路:触发器、寄存器、计数器等。

3、信号衰减和畸变:长的并行总线和控制线可能会发生交互串扰和传输线故障,表现为相邻的信号线出现尖峰脉冲(交互串扰),或驱动线上形成减幅振荡(相当于逻辑电平的多次转换),从而可能加入错误数据或控制信号。发生信号衰减的可能原因比较多,常见的有高湿度环境、长的传输线、高速率转换等。而大的电子干扰源会产生电磁干扰(EMI),导致信号畸变,引起电路的功能紊乱。

相关文章

- 详细阅读

- 详细阅读

-

想买家装类设计软件,移动端和电脑端详细阅读

家装设计软件哪个最好用 ? 现在的很多年轻人买了新房之后不知道如何进行装潢设计,脑子里除了大致想要的风格,其他都是一窍不通。而设计装潢并不是一件容易的事情,家具的摆放

-

要求使用面向对象的思想,设计一个学详细阅读

使用面向对象思想,定义一个学生类Student,该类包括以下字段:姓名name,学号stuNo和成绩score。packagecom.test;

publicclassStudent{

publicStringname;

publicStringstuNo;

pub -

Rave Reports 怎么找回已设计文件详细阅读

在RAVE中怎么样让标题在每一页显示呢?怎么样让标题在每一页显示呢? 选到TitleBand,在设置BandStyle在Print Occurrence把New page打勾选中,这样在预览你就会发现,这时生成的报表

-

做毕业设计用什么单片机好详细阅读

现在的主流8位单片机有哪些?51系列的,和avr系列的都有哪些?我大四做毕业设计用哪个型号的8位单8位单片机stc最新的STC15系列,AVR的可以ATmega16,ST的STM8S也挺好的,毕业设计还是使

-

郑州品策空间设计机构,服务怎么样?详细阅读

河南品策房地产营销策划有限公司怎么样?河南品策房地产营销策划有限公司是2016-05-25在河南省郑州市金水区注册成立的有限责任公司(自然人独资),注册地址位于郑州市金水区博颂

-

设计一子函数用选择排序法对10个元详细阅读

c++编写一个函数,用选择法对10个整数的数组进行排序。#include//标准输入输出函数调用需要此头文件、就是那个printf和scanf函数要用的 void main()//主函数 {int i,j,min,te

- 详细阅读

-

如何让你设计的IP形象更萌?详细阅读

如何设计一个受欢迎的IP形象?简单易记,品牌IP形象是需要长期去维护的,建议你找专业的设计公司去设计!找设计公司设计一个专属于自己品牌的吉祥物,可以少走许多弯路。 IP就是Intel