h81主板支持什么cpuH81主板采用了LGA1150处理器接口,因此只需要是LGA1150接口的处理器都可以使用,是目前英特尔的入门定位的主板。支持LGA 1150接口的赛扬G18xx、奔腾G3xxx、i

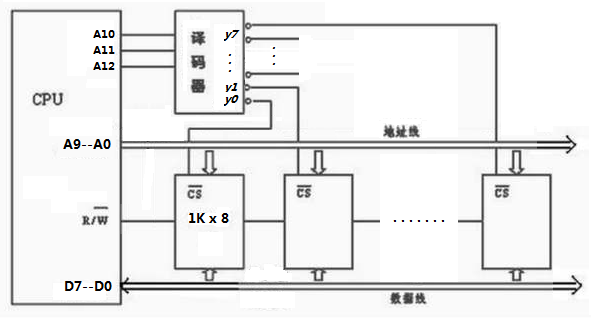

用1K*8的芯片构成4K*8的 存储器,并画出逻辑图

若用一k×8位的芯片组成四k×8位的存储器应选择什么译码器?

用1K×8位的芯片组成4K×8位的存储器,需要4片1K×8的芯片,译码器有4个输出端即可实现选片,所以可选择2线-4线译码器,74LS139就是。用1K×4位的DRAM芯片构成4K×8位存储器。问需要多少个这样的DRAM芯片?画出该存储器的组成逻辑框图。

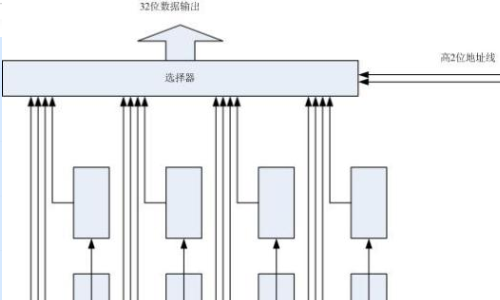

芯片数=总容量/容量=4k*8÷1k*4=8片。将每四zhidao块分为一组,形成32位的数据宽度,根据该储存容量大小一共需要16位地址线(可以根版据储存容量除以数据宽度来确定)。

将32K*8芯片组成128K*16的只读度器,所以首先位扩展将数据线8扩展到16,即D0~D15,然问后字扩展32K是15条地址线,128是17条地址线,所以要答用2/4译码器将地址线15扩展到17,需要用到的芯片是(128/32)*(16/8)=8,连接如图所示!红色为A0~A14的地址总线。

扩展资料:

用1K×4位的DRAM芯片构成4K×8位存储器。是一个64K 1bit的DRAM芯片,将8片并接起来,可以构成64KB的动态存储器。

每片只有一条输入数据线,而地址引脚只有8条。为了形成64K地址,必须在系统地址总线和芯片地址引线之间专门设计一个地址形成电路。使系统地址总线信号能分时地加到8个地址的引脚上,借助芯片内部的行锁存器、列锁存器和译码电路选定芯片内的存储单元,锁存信号也靠着外部地址电路产生。

当要从DRAM芯片中读出数据时,CPU 首先将行地址加在A0-A7上,而后送出RAS 锁存信号,该信号的下降沿将地址锁存在芯片内部。接着将列地址加到芯片的A0-A7上,再送CAS锁存信号,也是在信号的下降沿将列地址锁存在芯片内部。然后保持WE=1,则在CAS有效期间数据输出并保持。

这个用1K*8位的SRAM芯片组成一个8K*16位的存储器。图怎么画,急用!

共16个芯片,每个芯片10根地址线,并联,还需三根地址线可以作为3-8译码器的输入,3-8译码器8个输出作为16个芯片的片选,每2个芯片共用一个输出,8片的8 根数据线并联一起 另外8片的8 根数据线并联一起共有16根数据线。这个用1K*8位的SRAM芯片组成一个8K储存空间图需要几片,几根地址线,图怎样画,画出来有个照片?

一片就1K,要组成8K就需要8片;

1K=1024=2^10 --- 需要10根地址线;

8K=8192=2^13 --- 需要13根地址线;

低10根地址总线与每片芯片的A0~A9直接相连,称片内地址线;

高3根地址总线通过3/8译码器产生8个不同的片选信号,接各芯片的CS#端,称片选地址线。

满意采纳哈

用1K×4位的RAM芯片构成2K×8位的存储器,画出CPU和存储芯片的连接图.

分析:用1K×4位的RAM芯片构成2K×8位的存储器,1K×4位构成2K×8位单用字扩展或者单用位扩展无法解决问题,要字扩展和位扩展同时进行。画出CPU和存储芯片的连接图如下图:

1KB=2^10B,2KB=2^11B

扩展资料:

存储信息一般是存储在存储器(ROM、RAM)上的 。

在实际应用中,经常出现一片ROM或RAM芯片不能满足对存储器容量需求的情况,这就需要用若干片ROM或RAM组合起来形成一个存储容量更大的存储器。而组合方式有字扩展和位扩展两种。

用多片位宽相同的存储器(ROM或RAM)芯片扩展包含更多存储器的过程。一般是在每个字的位数够而字的数目不够时使用。

生产的存储器芯片容量有限,在字数或字长方面与实际存储器要求有所差距,所以要在字向与位向两方面进行扩充,才能满足实际存储器的要求。

cpu对存储器进行读写操作时,首先由地址总线给出地址信号,然后再发出有关进行读操作与写操作的控制信号,最后在数据总线上进行信息交换。

把用位数较少的多片存储器(ROM或RAM)组合成位数更多的存储器的扩展方法。位扩展只是扩展的位数。

参考资料来源:

百度百科-位扩展

百度百科-字扩展

相关文章

- 详细阅读

-

GA-880G-UD3H (rev. 1.x)芯片组驱详细阅读

技嘉880g-ud3h可以装win10系统吗观看主板是无法判断,不过一般电脑都可以安装win10,因为它运行时所需要的硬件资源是比较低,比win7和win8要求低。技嘉GA-880G-UD3H用哪个版本的

-

CDK开发环境内找不到W806芯片怎么详细阅读

wt61p806芯片故障wt61p806芯片故障解决方法是。

一般来说,电脑故障包括硬件损坏和软件程序错误两大类,前者属于硬故障,后者属于软故障。硬故障可分为器件故障、机械故障和人为 -

蒲公英组网如何通过计算机名访问详细阅读

如何用计算机名就能访问另一台计算机如果两台电脑用路由器上网,可以按下面方法设置,如果没有可以用网线和网卡连接。 用一根网线让两台电脑共享文件 网卡连接,首先准备好两张10

-

2sd882L是什么芯片详细阅读

三极管C3205可以用什么型号的三极管的代替c3205可以用c2655,d400,5609,c2500,c2060替换.一般电子市场都有得买直流电机驱动芯片的选择一、用的最多的一个H桥驱动芯片:L928N这

-

cjc311e是什么芯片详细阅读

现在买笔记本哪款性价比好?这取决于您的预算和使用需求。以下是一些性价比较高的笔记本电脑推荐:1. 小米笔记本Air 13.3:这是一款具有出色性价比的高性能笔记本电脑,配备了第八

-

计算机为什么不会运算规则?详细阅读

电脑自带的计算器不按数学运算法则计算了,怎么回事?Windows的计算器没有优先规则,也就是相当于逐个键入数字和运算符 当然只是按照输入的顺序计算计算机不做减法运算?计算机内部

- 详细阅读

-

为何个人电脑不需要多于一个CPU详细阅读

电脑为什么不装多个cpu?在电脑里多装cpu并不稀奇……在服务器领域早就实现了。 在个人电脑中,一台电脑配多个cpu,成本的提升是最大的阻碍……所以现在没有这样的应用,都是用多核

- 详细阅读