想在VB中根据数据库的数据画曲线变化图,如何画?用什么方法VB提供的绘制图形的方法:(可以在窗体上或PicTureBox控件上使用) 与你主题相关的有: 1,绘制直线 object.Line (x1,y1) - (x

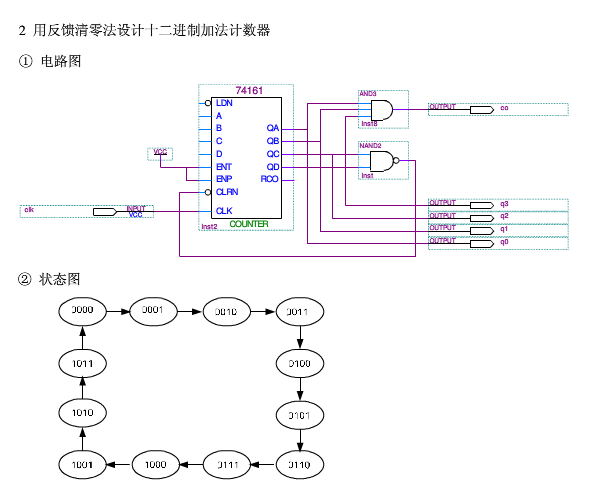

采用反馈清“0”零法设计一个模N=8的加法计数器,multisim

用74LS161设计模N=8的加法计数器,用反馈清零法。

用这个例子改一下就成8进制的了,状态图到0111回到0000

祝你好运!

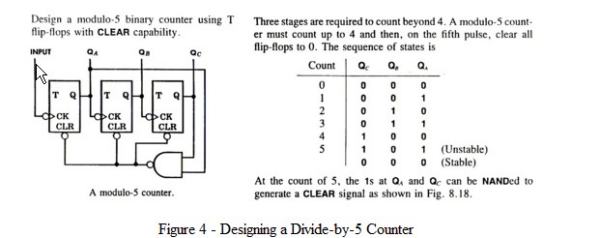

设计一个8位加法计数器电路(0.1....7循环)用t触发器实现,求个电路图

参考上图模5计数器,删去2输入与非门,电路就是一个模8计数器,Y(QcQbQa)=000,001,010......110,111,000........。

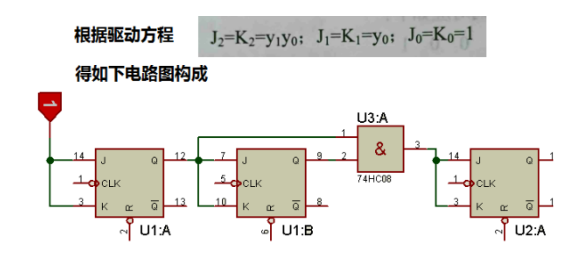

用JK触发器作为存储原件,设计一个模8加1计数器。求逻辑电路图。

逻辑电路图:

预置输入先置0,取Q(N)的输出做置数信号,在(N+1)的时钟前沿Q输出同步归零,这是完全同步计数,是同步计数器的正确用法。比较两种方法可知,设计N进制计数器时,清零法的反馈信号是(N+1),控制端是置零CR' ;置数法的反馈信号是 N ,控制端是置数LD' 。

扩展资料:

简单的逻辑电路通常是由门电路构成,也可以用三极管来制作,例如,一个NPN三极管的集电极和另一个NPN三极管的发射极连接,这就可以看作是一个简单的与门电路,即:当两个三极管的基极都接高电平的时候,电路导通,而只要有一个不接高电平,电路就不导通。

任何时刻输出信号的逻辑状态仅取决于该时刻输入信号的逻辑状态,而与输入信号和输出信号过去状态无关的逻辑电路。

由于组合逻辑电路的输出逻辑状态与电路的历史情况无关,所以它的电路中不包含记忆性电路或器件。门电路是组合逻辑电路的基本单元。当前组合逻辑电路都已制成标准化、系列化的中、大规模集成电路可供选用。

参考资料来源:百度百科-逻辑电路

求74LS192 用复位法及预置法设计模8加法计数器,需产生进位C。设计过程、状态转换图和逻辑电路图

用74LS192,采用复位法改成8进制计数器,当计数到8时,Q3为1,作为复位信号接到复位端MR,即可复位回0。所以,最大数是7,则利用Q2Q1Q0=111经与非门输出低电平作为进位C信号。逻辑图即仿真图如下。

反馈置数法,同样利用Q3产生置数信号加到PL端,进位信号同上。采纳后给第二个逻辑图。

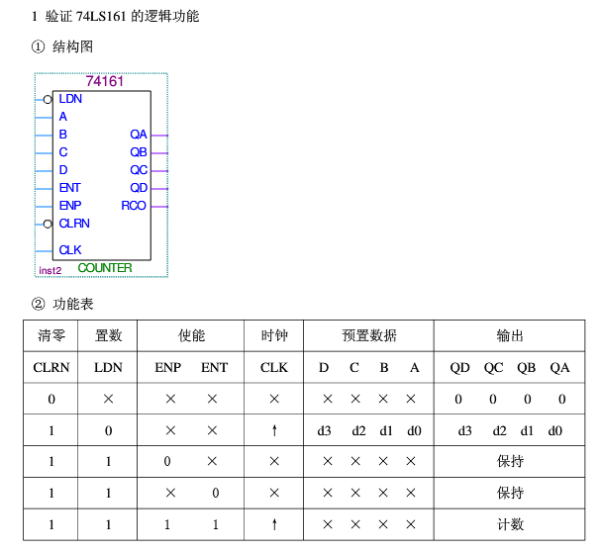

加法计数器74LS161

用同步加法计数器74LS161(或74LS160)和二4输入与非门74LS20构成百以内任意进制计数器,并采用LED数码管显示计数进制。采用555定时器构成多谐振荡电路,为同步加法计数器提供时钟输入信号。例如,采用同步加法计数器74LS 161构成60进制加法计数器的参考电路如图2所示。 图2 分析整个电路,可以将所需的逻辑功能设计过程分为三个部分,即加法计数器的设计,555定时器组成的多谐振荡器的设计,以及LED数码管显示进制的设计。 1. 加法计数器设计(清零法) 74LS161为十六进制四位二进制加法计数器,异步清零,同步置数。 设计60进制的加法计数器,采用清零法。60用二进制表示为0相关文章

- 详细阅读

-

python编程语言详细阅读

Python是什么编程语言?Python的底层语言是C。大多数高级语言都是在C语言的基础上开发的,比如Python、Java、C#……,这些的底层都是C。 Python是一种广泛使用的解释型、高级编程

-

MATLAB中图片上的字的像素位置与数详细阅读

我有一幅图片,在左下角建立直角坐标系,然后怎样用matlab找出我所需要的目标物的像素坐标?用ginput函数,就可以了。 第一是你把图片读入到MATLAB里, 再用hold on, [x,y]=gingput(2)

-

请问数学: 二进制怎么理解呢?比如,十详细阅读

怎么理解二进制二进制,是计算技术中广泛采用的一种数制,由德国数理哲学大师莱布尼茨于1679年发明。二进制数据是用0和1两个数码来表示的数。它的基数为2,进位规则是“逢二进一

-

杭州壹齐互联信息技术有限公司详细阅读

张杰的个人资料【个人简介】 英文名:Jason 昵称:张小杰、包子、小白、杰宝 小杰 性别:男 民族:汉族 籍贯:中国四川省成都市新都区新繁镇 生日:1982年12月20日 星座:射手座 身高:180C

-

请问有谁知道云南机场集团的信息技详细阅读

请问昆明长水机场信息技术员招聘笔试内容考什么?面试又涉及哪些内容呢笔试全是选择题,公共基础(跟事业单位考得差不多)50个单选,专业知识:80个单选,涉及计算机基础,计算机网络,操作系

-

花钟的A6信息技术的作用详细阅读

信息技术的作用信息技术的作用主要体现在以下几个方面: (1)推动经济的增长。在生产领域推广信息技术,可以改善劳动条件,扩大生产能力, 提高产品质量,增加经济效益。信息技术的发展,

-

南海信息技术学院狮山校区的电话。详细阅读

南海信息技术学校狮山校区的咨询电话?Tel:0757-85588786/85588710(大沥教务处) 86685603(狮山教务处)佛山的高中技校有哪几间?国家重点.. 一.佛山高级技工学校咯 有四个校区...

-

八年级上册信息技术 书本上的题详细阅读

八年级上册信息技术复习提纲2009学年海珠区八年级上学期信息技术期末测试题 学校: 班别: 姓名: 学号: 成绩: 1课时完成 一、选择题(每题2.5分,共50分) 1. 对于计算机网络,以下说法正

-

信息技术C++题求助详细阅读

信息技术,我感觉这道题应该是C吧?答案的确是C。 简单分析下: \是除法取整运算,Mod是除法取余运算。 N\10的结果剔除了个位,这个结果再除以10取余算出的就是十位上的数字了。 比如